|

Company: Tandem Computers, Inc.

Based: Cupertino California Founded: 1974, Now a server division of Hewlett Packard. Founder: James "Jimmy" Treybig Specialty: Leading manufacturer of fault-tolerant, mission critical, mainframe computer systems for ATM networks, banks, stock exchanges, telephone switching centers, and other commercial transaction processing applications requiring maximum up-time and zero data loss. Created the Tandem T/16 - worlds first fault-tolerant computer, & the Nonstop Himalaya & Cyclone series computers. |

History of CPU's used in Tandem Computers Systems

- 1976 Used their own 16-bit CPU design consisting of 2 boards with TTL Logic chips & SRAM memory (T/16 NonStop series)

- 1981 Added 32-bit support at microcode / software level, CPU consisting of 3 boards with TTL Logic chips and DRAM memory chips (NonStop II series)

- 1983 Added selective 32-bit support in hardware, CPU consisting of 4 boards with TTL & Programmed Array logic chips (NonStop II series with TXP CPU)

- 1986 Third generation CPU - consisting of 3 boards with ECL gate array chips running at 12 MHz (Nonstop VLX series)

- 1987 Moved to CPU consisting of one board with 6 compiled silicon ASIC CMOS chips (NonStop CLX series)

- 1990 Moved to their first single-chip processor, the MIPS R2000 RISC 32-bit microprocesor (Integrigrity S2 series). Each computer used 3 microprocessor chips for redundancy. The MIPS chips would initially be manufactured under license by either Integrated Device Technology (IDT), LSI Logic, Performance Semiconductor, and later - NEC or Siemens.

- 1991 Moved to the MIPS R3000 RISC 32-bit Microprocessor (NonStop Cyclone/R & CLX/R)

- 1993 Moved to the MIPS R4400 RISC 64-bit Microprocessor (NonStop Himalaya series). K series computers available with either 2 or 4 microprocessor chips.

- 1995 K2 series of entry-level Himalaya computers offered with either 2 or 4 of the MIPS R3000 RISC microprocessor chips.

- 1995 K200, K2000, K20000 Himalaya computers offered with MIPS R4400 RISC 64-bit Microprocessors.

- 2001 Moved to the Intel Itanium 64-bit Microprocessor (Compaq NonStop series)

- 2008 Added support for multiple core Microprocessors (HP Integrity series)

Tandem Computers MIPS RISC Processor Paperweight (1991)

Item #823 (#837 similar)

Paperweight contains a Tandem Computers MIPS based RISC microprocessor embedded in Lucite.

Starting in 1991, Tandem Computers started using single chip MIPS RISC Microprocessors to power their fault tolerant computer systems. Before this, they were using CPU's that were composed of multiple PCB boards that contained an array of individual logic & memory chips as wells as other discrete electronic components.

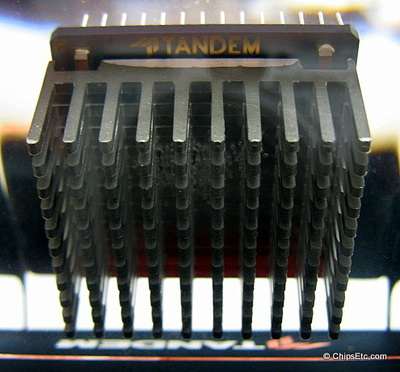

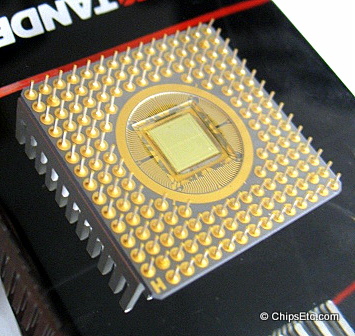

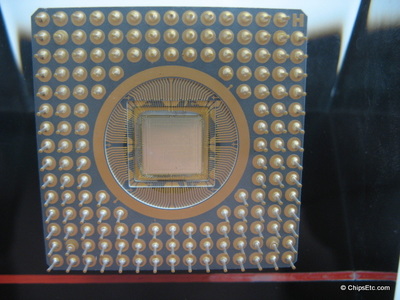

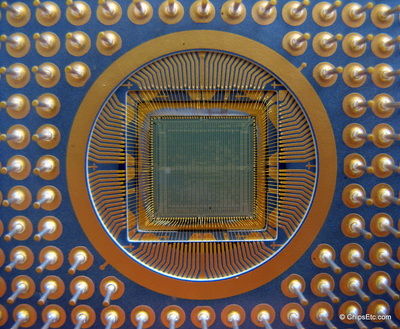

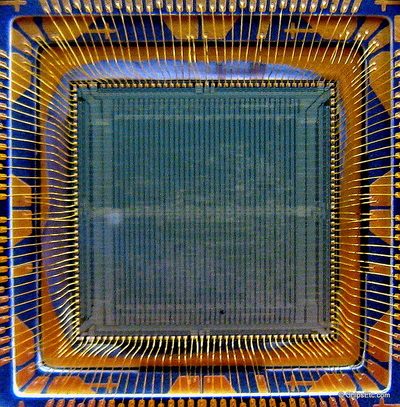

This MIPS chip is mounted in a PGA (Pin Grid Array) Ceramic package with 155 gold plated pins. The underside cap has been removed in order to allow viewing of the silicon die and gold wire bonding. On the top side of the chip's package is a finned aluminum heat-sink for air-cooling. The processor is marked "Tandem" on it's topside near the heatsink.

Tandem Computers mainframes used multiple (from 2 to 16) processors in their systems to insure a high level of fault tolerance (Later systems could have up to 4000 CPU's). If any one of the processors failed then the operating system automatically shifted it's workload to the other processors. Each processor had it's own private memory, I/O processor, and copy of the operating system microcode in it to allow for advanced fault isolation.

Starting in 1991, Tandem Computers started using single chip MIPS RISC Microprocessors to power their fault tolerant computer systems. Before this, they were using CPU's that were composed of multiple PCB boards that contained an array of individual logic & memory chips as wells as other discrete electronic components.

This MIPS chip is mounted in a PGA (Pin Grid Array) Ceramic package with 155 gold plated pins. The underside cap has been removed in order to allow viewing of the silicon die and gold wire bonding. On the top side of the chip's package is a finned aluminum heat-sink for air-cooling. The processor is marked "Tandem" on it's topside near the heatsink.

Tandem Computers mainframes used multiple (from 2 to 16) processors in their systems to insure a high level of fault tolerance (Later systems could have up to 4000 CPU's). If any one of the processors failed then the operating system automatically shifted it's workload to the other processors. Each processor had it's own private memory, I/O processor, and copy of the operating system microcode in it to allow for advanced fault isolation.

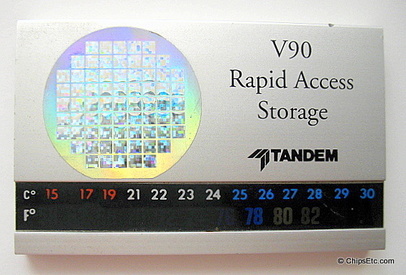

Tandem Computer V90 Memory Storage Wafer Paperweight (1991)

Item #824

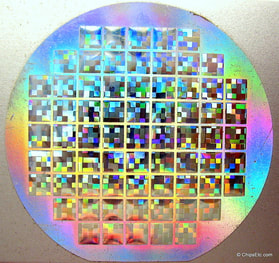

Aluminum paperweight from Tandem Computers features a small holographic replica of a multi-chip Silicon Wafer that would have been the type of memory storage used in their V90 mass storage system. It was designed to be used with Tandem Computer's high-end NonStop Cyclone mainframe computer systems.

The V90 Rapid Access Storage subsystem was the computer industry's first commercial solid-state storage subsystem based on whole-wafer, WSI (Water scale integration) technology. The basic memory size of the V90 was 40 MB, each memory model being formed from two 6" silicon wafers.

The V90 storage subsystem used memory technology designed by Anamartic Ltd. and was fabricated by Fujitsu. The memory was constructed from an entire, uncut Silicon wafer with circuitry designed to detect and route around faulty cells.

At the bottom of this desktop paperweight is a temperature strip for showing room temperature.

The V90 Rapid Access Storage subsystem was the computer industry's first commercial solid-state storage subsystem based on whole-wafer, WSI (Water scale integration) technology. The basic memory size of the V90 was 40 MB, each memory model being formed from two 6" silicon wafers.

The V90 storage subsystem used memory technology designed by Anamartic Ltd. and was fabricated by Fujitsu. The memory was constructed from an entire, uncut Silicon wafer with circuitry designed to detect and route around faulty cells.

At the bottom of this desktop paperweight is a temperature strip for showing room temperature.